コラム

|

第14回 「最近の研究から」 中島 安理 >> 研究室ホームページ |

現在フラッシュメモリは100nmを割るデバイスサイズ領域に入っています。フラッシュメモリにおけるフローティングゲートのサイズが小さくなると、フローティングゲートに保持する電子数も小さくなります。この電子数が小さくなると、フローティングゲートを囲む絶縁膜にわずかの電子リークパスがあっても電子が短時間で失われ電子を保持できなくなり、メモリの役目を果たせなくなります。これを解決するために、フローティングゲートを複数のドットに分割する事が提案されています。そうすれば、複数のフローティングドットの内のいくつかにリークパスがあっても、正常なドットがどこかに残っていれば全体としてはある程度電子リークの度合いを低減できるからです。しかし今までは未だ、リークの影響を最も低減できるドットの最適な配置についてわかっていませんでした。そこで私の研究室では、電子線リソグラフィーを用いる事により、フローティングドットのサイズ、個数、配置を正確に規定して、それらのメモリ特性への影響を系統的に調べました。

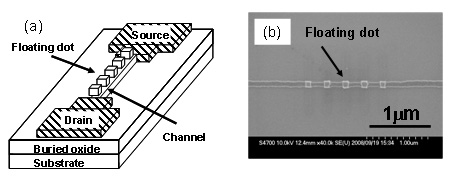

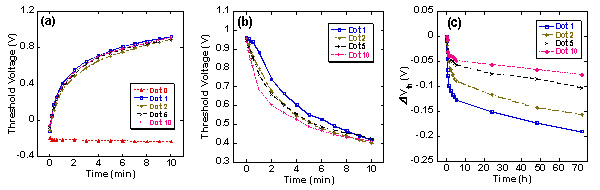

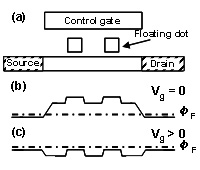

その結果、フローティングドットをチャネル方向に複数直列に配置した場合に(図1)、書き込み・消去特性を劣化させずに、保持時間を長くできる事が明らかになりました(図2)。これは次のような理由のためであると解釈できます。このような構造について電子を保持している場合には、電流の流れる通路であるチャネルにおける伝導帯端のエネルギーが最も高くなる位置はそれぞれのドットの直下となります(図3(a),(b))。この最も高い伝導帯端エネルギーとソース・ドレインのフェルミエネルギーとの差がしきい値電圧を決めるので(図3(c))、複数のドットの内のいくつかにリークがあり、そこでの伝導帯端エネルギーが下がっても、リークの無いドットが1つでもあれば全体としてのしきい値電圧は全く変わりません。このためメモリの保持時間を長く保てます。一方、書き込み時には、複数のドットに同時にコントロールゲートから高電圧がかかるので書き込み時間は変わりません。通常のフラッシュメモリでは書き込み・消去特性と保持特性はトレードオフの関係にあるので、これはフラッシュメモリの最適構造に関する指針を与える画期的な成果です。この結果は2008年のApplied Physics Letter及び2009年のJournal of Applied Physicsに掲載されました。

図1 ドットメモリの最適構造(a)とその平面SEM(b)

図2 書き込み特性(a)と消去特性(b)と保持特性(c)のドット数依存性

図3 エネルギーダイヤグラム